Bandwidth antarmuka

Standar Gigabit Ethernet menggunakan kabel Kategori 5 (Unshielded Twisted Pair) sebagai media transmisi, dijelaskan dalam IEEE 802.3ab, akhirnya disetujui pada 28 Juni 1999.

Waktu telah berlalu, dan sekarang kita sudah dapat mengatakan bahwa gigabit Ethernet melalui "tembaga" telah dengan kuat memasuki sejarah pengembangan jaringan lokal. Penurunan tajam harga untuk adaptor jaringan gigabit 1000Base-T dan modul gigabit untuk sakelar secara bertahap mengarah pada fakta bahwa pemasangan adaptor semacam itu di server menjadi standar de facto. Misalnya, beberapa produsen server telah mulai mengintegrasikan adaptor gigabit 1000Base-T ke dalam server motherboard, dan jumlah perusahaan yang memproduksi adaptor tersebut mencapai 25 pada awal tahun ini. Selain itu, adaptor yang dirancang untuk pemasangan di stasiun kerja mulai diproduksi (mereka berbeda karena dirancang untuk bus PCI 32-bit 33-MHz) . Semua ini memungkinkan kita untuk mengatakan dengan yakin bahwa dalam satu atau dua tahun adaptor jaringan gigabit akan menjadi biasa seperti adaptor Fast Ethernet sekarang.

Pertimbangkan inovasi mendasar yang diwujudkan dalam standar IEEE 802.3ab dan yang memungkinkan untuk mencapai kecepatan transmisi yang begitu tinggi, sambil mempertahankan jarak maksimum yang sama antara dua komputer 100 m, seperti yang terjadi pada standar Fast Ethernet.

Pertama-tama, kita ingat bahwa adapter jaringan beroperasi pada lapisan fisik dan tautan data dari model tujuh lapis OSI (Interkoneksi Sistem Terbuka). Lapisan tautan biasanya dibagi menjadi dua sublapisan: MAC dan LCC. Sublapisan MAC (Kontrol Akses Media) adalah sublevel kontrol akses ke media transmisi data, yang memastikan pembagian yang benar dari media transmisi data bersama yang umum, menyediakannya sesuai dengan algoritma tertentu pada pembuangan stasiun tertentu. Sublayer LCC (Logical Link Control) bertanggung jawab untuk transmisi frame antar node dengan berbagai tingkat keandalan, dan juga mengimplementasikan fungsi antarmuka dengan lapisan ketiga (jaringan) yang berdekatan dengannya.

Semua perbedaan antara Ethernet dan Fast Ethernet hanya terkonsentrasi pada lapisan fisik. Pada saat yang sama, MAC dan LCC tidak mengalami perubahan apa pun.

Lapisan fisik secara kasar dapat dibagi menjadi tiga elemen: lapisan negosiasi, antarmuka independen media (MII) dan perangkat lapisan fisik (PHY). Perangkat lapisan fisik juga dapat dibagi menjadi beberapa sublapisan: sublapisan pengkodean fisik, sublapisan Lampiran Medium Fisik, sublapisan Tergantung Media Fisik, dan sublapisan Negosiasi Otomatis.

Jika perbedaan antara Ethernet dan Fast Ethernet minimal dan tidak mempengaruhi lapisan MAC, maka ketika mengembangkan standar Gigabit Ethernet 1000Base-T, pengembang tidak hanya harus membuat perubahan pada lapisan fisik, tetapi juga mempengaruhi lapisan MAC (Gbr. .1).

Namun demikian, ada banyak kesamaan antara ketiga teknologi tersebut. Pertama-tama, ini adalah metode akses ke media transmisi data CSMA / CD, mode operasi half-duplex dan full-duplex, serta format frame Ethernet. Pada saat yang sama, penggunaan kabel twisted-pair Kategori 5 memerlukan perubahan besar pada implementasi lapisan fisik adaptor.

Masalah pertama dengan menerapkan 1 Gbps adalah untuk memastikan diameter jaringan yang dapat diterima saat beroperasi dalam mode setengah dupleks. Seperti yang Anda ketahui, ukuran bingkai minimum di Jaringan Ethernet dan Fast Ethernet adalah 64 byte. Namun, ukuran bingkai 64 byte pada kecepatan transfer 1 GB/s mengarah pada fakta bahwa untuk deteksi tabrakan yang andal, diperlukan diameter jaringan maksimum (jarak antara dua komputer yang paling jauh satu sama lain) tidak lebih dari 25 m deteksi tabrakan yang berhasil hanya mungkin jika waktu antara pengiriman dua frame berturut-turut dengan panjang minimum lebih besar dari dua kali waktu propagasi sinyal antara dua node paling jauh dalam jaringan. Oleh karena itu, untuk memberikan diameter jaringan maksimum 200 m (dua kabel 100 m dan satu sakelar), panjang bingkai minimum dalam standar Gigabit Ethernet telah ditingkatkan menjadi 512 byte. Untuk menambah panjang bingkai ke panjang yang diperlukan, adaptor jaringan mengisi bidang data dengan panjang 448 byte dengan apa yang disebut ekstensi. Bidang ekstensi adalah bidang yang diisi dengan karakter terlarang yang tidak dapat disalahartikan sebagai kode data (Gbr. 2). Pada saat yang sama, peningkatan panjang bingkai minimum memiliki efek negatif pada transmisi pesan layanan pendek, seperti penerimaan, karena informasi yang ditransmisikan yang berguna menjadi jauh lebih sedikit daripada total informasi yang ditransmisikan. Untuk mengurangi overhead saat menggunakan frame panjang untuk mengirimkan penerimaan pendek, standar Gigabit Ethernet memungkinkan transmisi beberapa frame berturut-turut dalam mode penangkapan eksklusif media, yaitu, tanpa mentransfer media ke stasiun lain. Seperti rezim eksklusif menangkap disebut Burst Mode. Dalam mode ini, stasiun dapat mengirimkan beberapa frame berturut-turut dengan panjang total tidak lebih dari 8192 byte (BurstLength).

Sebagaimana telah disebutkan, seiring dengan perubahan pada lapisan MAC, pencapaian kecepatan transmisi gigabit menjadi mungkin karena perubahan yang signifikan pada lapisan fisik, yaitu teknologi penyajian data (coding) selama transmisi data melalui twisted pair.

Untuk memahami perubahan yang telah dibuat pada tingkat fisik, mari kita ingat apa itu kabel data dan gangguan apa yang terjadi selama transmisi sinyal.

Kabel unshielded kategori 5 terdiri dari empat pasang kabel, dengan masing-masing pasangan dipilin bersama. Kabel semacam itu dirancang untuk beroperasi pada frekuensi 100 MHz (Gbr. 3).

Diketahui dari kursus fisika bahwa setiap kabel memiliki, selain resistansi aktif, juga kapasitif dan induktif, dua yang terakhir tergantung pada frekuensi sinyal. Ketiga jenis resistansi menentukan apa yang disebut impedansi rangkaian. Kehadiran impedansi mengarah pada fakta bahwa ketika sinyal merambat di sepanjang kabel, ia secara bertahap melemah, kehilangan sebagian dari kekuatan aslinya.

Jika induksi timbal balik dihitung di awal kabel, maka jenis interferensi yang sesuai akan disebut NEXT (Near-end crosstalk loss). Jika interferensi yang disebabkan oleh induksi timbal balik dianggap di ujung kabel, maka mereka disebut FEXT (Far-end crosstalk loss - Gbr. 4).

Selain itu, selama perambatan sinyal, jenis gangguan lain terjadi, terkait dengan ketidakcocokan impedansi input penyesuai jaringan dan kabel. Akibat ketidakcocokan ini, terjadi pantulan sinyal, yang juga mengarah pada pembentukan noise.

Transmisi sinyal di bawah kondisi interferensi yang dijelaskan di atas memerlukan penggunaan metode yang cerdik untuk memastikan tingkat transmisi yang diperlukan dan pada saat yang sama memastikan pengenalan sinyal yang ditransmisikan tanpa kesalahan.

Pertama-tama, mari kita ingat metode apa yang digunakan untuk mewakili sinyal informasi.

Saat mengkodekan bit "nol" dan "satuan" secara digital, baik kode potensial atau pulsa digunakan. Dalam kode potensial (Gbr. 5), hanya nilai potensial sinyal yang digunakan untuk mewakili nol dan satu logis. Misalnya, satu direpresentasikan sebagai potensi tingkat tinggi, dan nol direpresentasikan sebagai potensi level rendah. Kode pulsa memungkinkan bit diwakili oleh penurunan potensial dalam arah tertentu. Jadi, penurunan potensial dari level rendah ke level tinggi dapat sesuai dengan nol logis.

Saat menggunakan pulsa persegi panjang untuk transmisi data, perlu untuk memilih metode pengkodean yang secara bersamaan memenuhi beberapa persyaratan.

Pertama, pada bit rate yang sama, ia akan memiliki lebar spektrum terkecil dari sinyal yang dihasilkan.

Kedua, dia akan memiliki kemampuan untuk mengenali kesalahan.

Ketiga, akan menyediakan sinkronisasi antara penerima dan pemancar.

Kode NRZ

Dalam kasus pengkodean potensial yang paling sederhana, yang logis dapat diwakili oleh potensi tinggi, dan nol logis dengan potensi rendah. Cara yang sama untuk merepresentasikan sinyal disebut "coding without return to zero, atau coding NRZ (Non Return to Zero)". Istilah "tidak kembali" dalam hal ini berarti bahwa selama seluruh interval jam tidak ada perubahan pada level sinyal. Metode NRZ mudah diterapkan, memiliki pengenalan kesalahan yang baik, tetapi tidak memiliki properti sinkronisasi sendiri. Kurangnya sinkronisasi diri mengarah pada fakta bahwa ketika urutan panjang nol atau satu muncul, penerima tidak dapat menentukan dari sinyal input titik-titik waktu ketika perlu untuk membaca data lagi. Oleh karena itu, sedikit ketidaksesuaian antara frekuensi clock penerima dan pemancar dapat menyebabkan kesalahan jika penerima membaca data pada waktu yang salah saat dibutuhkan. Fenomena ini sangat penting pada kecepatan transmisi tinggi, ketika waktu satu pulsa sangat singkat (pada kecepatan transmisi 100 Mbps, waktu satu pulsa adalah 10 ns). Kerugian lain dari kode NRZ adalah adanya komponen frekuensi rendah dalam spektrum sinyal ketika urutan panjang nol atau satu muncul. Oleh karena itu, kode NRZ tidak digunakan dalam bentuk murni untuk transmisi data.

kode NRZI

Jenis pengkodean lainnya adalah kode NRZ yang sedikit dimodifikasi yang disebut NRZI (Non Return to Zero with one Inverted). Kode NRZI adalah implementasi paling sederhana dari perubahan level sinyal atau prinsip pengkodean diferensial. Dengan pengkodean ini, ketika nol ditransmisikan, level sinyal tidak berubah, yaitu potensi sinyal tetap sama seperti pada siklus sebelumnya. Ketika satu unit ditransfer, potensi dibalikkan ke kebalikannya. Perbandingan kode NRZ dan NRZI menunjukkan bahwa kode NRZI memiliki sinkronisasi diri yang lebih baik jika ada lebih banyak yang logis dalam informasi yang dikodekan daripada nol logis. Dengan demikian, kode ini memungkinkan Anda untuk "bertarung" dengan urutan yang panjang, tetapi tidak memberikan sinkronisasi diri yang tepat ketika urutan panjang dari nol logis muncul.

Kode Manchester

Dalam kode Manchester, perbedaan potensial digunakan untuk mengkodekan nol dan satu, yaitu pengkodean dilakukan oleh bagian depan pulsa. Penurunan potensial terjadi di tengah pulsa clock, sedangkan unit dikodekan oleh penurunan dari potensial rendah ke tinggi, dan nol sebaliknya. Pada awal setiap siklus, jika muncul beberapa nol atau satu berturut-turut, penurunan potensial layanan dapat terjadi.

Dari semua kode yang telah kami pertimbangkan, Manchester memiliki sinkronisasi mandiri terbaik, karena transisi sinyal terjadi setidaknya sekali per siklus clock. Itulah sebabnya kode Manchester digunakan dalam jaringan Ethernet dengan kecepatan transmisi 10 Mbps (10Base 5, 10Base 2, 10Base-T).

Kode MLT-3

Kode MLT-3 (Multi Level Transmission-3) diimplementasikan mirip dengan kode NRZI. Perubahan level sinyal linier hanya terjadi jika input encoder adalah 1, namun, tidak seperti kode NRZI, algoritma pembangkitan dipilih sedemikian rupa sehingga dua perubahan yang berdekatan selalu memiliki arah yang berlawanan. Kerugian dari kode MLT-3 sama dengan kode NRZI - kurangnya sinkronisasi yang tepat ketika urutan nol logis yang panjang muncul.

Seperti yang telah dicatat, kode yang berbeda berbeda satu sama lain tidak hanya dalam tingkat sinkronisasi sendiri, tetapi juga dalam lebar spektrum. Lebar spektrum sinyal ditentukan terutama oleh harmonik yang memberikan kontribusi energi utama pada pembentukan sinyal. Harmonik dasar mudah dihitung untuk setiap jenis kode. Dalam kode NRZ atau NRZI, frekuensi maksimum harmonik fundamental (Gbr. 6) sesuai dengan urutan periodik nol logis dan satu, yaitu, ketika beberapa nol atau satu tidak terjadi secara berurutan. Dalam hal ini, periode harmonik dasar sama dengan interval waktu dua bit, yaitu, pada kecepatan transmisi 100 Mbps, frekuensi harmonik dasar harus 50 Hz.

Dalam kode Manchester, frekuensi maksimum harmonik fundamental sesuai dengan situasi ketika urutan panjang nol memasuki input encoder. Dalam hal ini, periode harmonik fundamental sama dengan interval waktu satu bit, yaitu, pada kecepatan transmisi 100 Mbps, frekuensi maksimum harmonik fundamental adalah 100 Hz.

Dalam kode MLT-3, frekuensi maksimum harmonik fundamental (Gbr. 7) dicapai ketika urutan panjang unit logis diumpankan ke input encoder. Dalam hal ini, periode harmonik fundamental sesuai dengan interval waktu empat bit. Oleh karena itu, pada kecepatan transmisi 100 Mbps, frekuensi fundamental maksimum adalah 25 MHz.

Seperti yang telah dicatat, pengkodean Manchester digunakan dalam jaringan Ethernet 10 Mbps, yang dikaitkan dengan sifat sinkronisasi mandiri yang baik dari kode dan frekuensi maksimum yang diizinkan dari harmonik dasar, yang, ketika beroperasi pada kecepatan 10 Mbps, akan menjadi 10MHz. Nilai ini cukup untuk kabel tidak hanya dari yang ke-5, tetapi juga dari kategori ke-3, yang dirancang untuk frekuensi 20 MHz.

Pada saat yang sama, penggunaan pengkodean Manchester untuk jaringan berkecepatan lebih tinggi (100 Mbps, 1 Gbps) tidak dapat diterima, karena kabel tidak dirancang untuk beroperasi pada frekuensi tinggi tersebut. Oleh karena itu, kode lain (NRZI dan MLT-3) digunakan, tetapi kode tersebut dikenai pemrosesan tambahan untuk meningkatkan sifat sinkronisasi sendiri dari kode tersebut.

Kode berlebihan

Pemrosesan tambahan semacam itu terdiri dari pengkodean blok logis, ketika satu kelompok bit digantikan oleh kelompok lain sesuai dengan algoritma tertentu. Jenis pengkodean yang paling umum adalah kode redundan 4B/5B, 8B/6T dan 8B/10T.

Dalam kode-kode ini, kelompok bit asli diganti dengan yang baru, tetapi kelompok yang lebih panjang. Dalam kode 4B/5B, sekelompok empat bit dipetakan ke sekelompok lima bit. Timbul pertanyaan - mengapa kita membutuhkan semua komplikasi ini? Faktanya adalah bahwa pengkodean seperti itu berlebihan. Misalnya, dalam kode 4B/5B, dalam urutan asli empat bit, ada 16 kombinasi bit yang berbeda dari nol dan satu, dan dalam kelompok lima bit sudah ada 32 kombinasi tersebut.Oleh karena itu, dalam kode yang dihasilkan, anda dapat memilih 16 kombinasi seperti itu yang tidak mengandung banyak nol (ingat bahwa dalam kode sumber NRZI dan MLT-3 urutan panjang nol menyebabkan hilangnya sinkronisasi). Dalam hal ini, kombinasi yang tidak digunakan yang tersisa dapat dianggap sebagai urutan terlarang. Jadi, selain meningkatkan sifat sinkronisasi sendiri Kode sumber pengkodean yang berlebihan memungkinkan penerima untuk mengenali kesalahan, karena terjadinya urutan bit terlarang menunjukkan terjadinya kesalahan. Korespondensi kode awal dan kode yang dihasilkan menghasilkan tab. satu .

Dapat dilihat dari tabel bahwa setelah menggunakan kode 4B/5B redundan, urutan yang dihasilkan tidak mengandung lebih dari dua nol berturut-turut, yang menjamin sinkronisasi sendiri dari urutan bit.

Dalam kode 8B/6T, urutan delapan bit dari informasi asli digantikan oleh urutan enam sinyal, yang masing-masing dapat mengambil tiga keadaan. Ada 256 status berbeda dalam urutan delapan bit, dan dalam urutan enam sinyal tiga tingkat sudah ada 729 status seperti itu (3 6 = 729), jadi 473 status dianggap dilarang.

Dalam kode 8B/10T, setiap urutan delapan bit diganti dengan urutan sepuluh bit. Dalam hal ini, urutan asli berisi 256 kombinasi nol dan satu yang berbeda, dan urutan yang dihasilkan berisi 1024. Jadi, 768 kombinasi dilarang.

Semua kode yang dianggap berlebihan digunakan dalam jaringan Ethernet. Dengan demikian, kode 4B/5B digunakan dalam standar 100Base-TX, dan kode 8B/6T digunakan dalam standar 100Base-4T, yang praktis tidak digunakan lagi. Kode 8B/10T digunakan dalam standar 1000Base-X (bila serat digunakan sebagai media transmisi).

Selain penggunaan pengkodean yang berlebihan, metode lain untuk meningkatkan sifat awal kode juga banyak digunakan - inilah yang disebut pengacakan.

Berebut

Pengacakan (scramble - mixing) adalah mencampur urutan asli nol dan satu untuk meningkatkan karakteristik spektral dan sifat sinkronisasi diri dari urutan bit yang dihasilkan. Pengacakan dilakukan dengan bitwise eksklusif OR (XOR) dari urutan asli dengan urutan pseudo-acak. Hasilnya adalah aliran "terenkripsi", yang dipulihkan di sisi penerima menggunakan descrambler.

Dari sudut pandang perangkat keras, pengacak terdiri dari beberapa gerbang XOR dan register geser. Ingat bahwa elemen logika XOR (exclusive OR) bekerja pada dua operan Boolean x dan y, yang dapat mengambil nilai 0 atau 1, operasi logika berdasarkan tabel kebenaran (Tabel 2).

Properti utama dari operasi XOR berikut langsung dari tabel ini:

Selain itu, mudah untuk melihat bahwa hukum kombinasi berlaku untuk operasi XOR:

Dalam diagram, elemen logika XOR biasanya dilambangkan seperti yang ditunjukkan pada Gambar. delapan .

Seperti yang telah disebutkan, komponen lain dari pengacak adalah register geser. Register geser terdiri dari beberapa sel penyimpanan dasar yang dihubungkan secara seri satu sama lain, dibuat berdasarkan rangkaian pemicu dan mentransmisikan sinyal informasi dari input ke output melalui sinyal kontrol - pulsa waktu. Register geser dapat merespons baik tepi positif pulsa clock (yaitu, ketika sinyal kontrol berpindah dari keadaan 0 ke keadaan 1), dan ke tepi negatif.

Pertimbangkan sel penyimpanan paling sederhana dari register geser, dikendalikan oleh tepi positif dari pulsa clock C (Gbr. 9).

Pada saat mengubah pulsa waktu dari keadaan 0 ke keadaan 1, sinyal yang ada pada inputnya pada saat waktu sebelumnya ditransmisikan ke output sel, yaitu ketika sinyal kontrol C sama dengan 0. Setelah itu, status keluaran tidak berubah (sel terkunci) hingga kedatangan tepi positif berikutnya dari pulsa clock.

Menggunakan rantai yang terdiri dari beberapa sel memori yang terhubung secara berurutan dengan sinyal kontrol yang sama, dimungkinkan untuk membuat register geser (Gbr. 10), di mana bit informasi akan ditransmisikan secara berurutan dari satu sel ke sel lain secara sinkron di sepanjang tepi positif dari pulsa jam.

Elemen integral dari pengacak apa pun adalah generator urutan acak semu. Generator semacam itu dibentuk dari register geser saat membuat umpan balik antara input dan output sel penyimpanan register geser melalui elemen logika XOR.

Pertimbangkan generator urutan pseudo-acak yang ditunjukkan pada Gambar. sebelas . Biarkan pada saat awal waktu keempat sel memori menyimpan beberapa keadaan yang telah ditentukan sebelumnya. Sebagai contoh, kita dapat mengasumsikan bahwa Q1=1, Q2=0, Q3=0 dan Q4=1, dan pada input sel pertama D=0. Setelah kedatangan pulsa waktu, semua bit akan bergeser satu bit, dan sinyal akan tiba di input D, yang nilainya akan ditentukan oleh rumus:

Dengan menggunakan rumus ini, mudah untuk menentukan nilai keluaran sel penyimpanan pada setiap siklus clock generator. Di meja. 3 menunjukkan keadaan keluaran sel memori dari generator urutan acak semu pada setiap siklus operasi. Pada saat yang sama, mudah untuk melihat bahwa pada saat awal waktu dan setelah 15 siklus, keadaan generator diulang sepenuhnya, yaitu, 15 siklus kerja adalah periode pengulangan dari urutan acak semu kami (itu adalah dari adanya periode pengulangan sehingga urutannya disebut pseudo-acak). Secara umum, jika generator terdiri dari n sel, periode pengulangannya adalah:

Generator yang kami anggap menggunakan beberapa keadaan awal sel yang sewenang-wenang, yaitu, memiliki preset. Namun, alih-alih preset seperti itu, pengacak sering menggunakan urutan asli itu sendiri, yang diacak. Pengacak seperti itu disebut sinkronisasi sendiri. Contoh pengacak seperti itu ditunjukkan pada Gambar. 12 .

Jika kita menentukan digit biner dari kode sumber, yang diterima pada siklus kerja ke-i pada input pengacak, melalui Ai , dan digit biner dari kode yang dihasilkan diperoleh pada siklus kerja ke-i, melalui B i , maka mudah untuk melihat bahwa pengacak yang dipertimbangkan melakukan operasi logis berikut: , di mana B i -3 dan B i -4 - digit biner dari kode yang dihasilkan masing-masing diperoleh pada siklus pengacak sebelumnya, 3 dan 4 siklus lebih awal dari momen saat ini.

Setelah decoding urutan yang diperoleh, descrambler digunakan di sisi penerima. Yang paling menakjubkan adalah bahwa rangkaian descrambler benar-benar identik dengan rangkaian pengacak. Tidak sulit untuk memverifikasi bahwa memang demikian halnya dengan penalaran sederhana. Jika kita menyatakan dengan B i digit biner dari kode sumber yang tiba pada siklus kerja ke-i pada input descrambler, dan digit biner dari kode yang dihasilkan diperoleh pada siklus kerja ke-i, dengan C i , maka descrambler, bekerja sesuai dengan skema yang sama seperti pengacak harus menerapkan algoritma berikut:

Oleh karena itu, jika skema descrambler cocok dengan skema pengacak, maka descrambler sepenuhnya mengembalikan urutan bit informasi asli.

Sirkuit pengacak empat bit yang dipertimbangkan adalah salah satu yang paling sederhana. Teknologi 1000Base-T menggunakan pengacak 33-bit yang jauh lebih kompleks, yang meningkatkan periode pengulangan menjadi 8.589.934.591 bit (2 33 -1), yaitu, urutan pseudo-acak yang dihasilkan diulang setiap 68,72 detik.

Pengkodean PAM-5

Setelah mengetahui kode apa yang digunakan untuk merepresentasikan data, dan mempertimbangkan metode untuk meningkatkan self-clocking dan sifat spektral dari kode ini, kami akan mencoba mencari tahu apakah tindakan ini cukup untuk memastikan transmisi data pada kecepatan 1000 Mbps menggunakan kabel Kategori 5 empat pasang.

Seperti yang telah dicatat, pengkodean Manchester memiliki sifat sinkronisasi diri yang baik dan dalam hal ini tidak memerlukan modifikasi apa pun, namun, frekuensi maksimum harmonik dasar secara numerik sama dengan kecepatan data, yaitu jumlah bit yang ditransmisikan per detik. Ini cukup untuk transmisi data pada kecepatan 10 Mbps, karena kabel kategori ke-3 (dan dalam standar 10Base-T kabel semacam itu dapat digunakan) terbatas pada frekuensi 16 MHz. Namun, pengkodean Manchester tidak cocok untuk kecepatan transfer data 100 Mbps atau lebih tinggi.

Penggunaan kode NRZI, setelah penyempurnaan lebih lanjut dengan kode blok 4B/5B redundan dan pengacakan, serta kode MLT-3 tiga posisi (untuk mengurangi frekuensi maksimum harmonik fundamental), memungkinkan data ditransmisikan pada kecepatan 100 Mbps melalui kabel Kategori 5. Memang, ketika menggunakan kode MLT-3, frekuensi maksimum harmonik dasar secara numerik sama dengan seperempat dari kecepatan transfer data, yaitu, pada kecepatan transmisi 100 Mbps, frekuensi dasar tidak melebihi 25 MHz, yang cukup untuk kabel Kategori 5. Namun, metode ini tidak cocok untuk transmisi data pada kecepatan 1000 Mbps.

Oleh karena itu, standar 1000Base-T menggunakan metode pengkodean yang berbeda secara mendasar. Untuk penurunan frekuensi jam hingga nilai yang memungkinkan data ditransmisikan melalui pasangan bengkok kategori 5, data pada saluran diwakili dalam apa yang disebut kode PAM-5 (Gbr. 13). Di dalamnya, sinyal yang ditransmisikan memiliki satu set lima level tetap (-2, -1, 0, +1, +2). Empat di antaranya digunakan untuk mengkodekan bit informasi, dan yang kelima untuk koreksi kesalahan. Pada satu set empat level tetap, satu status sinyal diskrit dapat mengkodekan dua bit informasi sekaligus, karena kombinasi dua bit memiliki empat kemungkinan kombinasi (disebut dibit) - 00, 01, 10 dan 11.

Beralih ke dibit memungkinkan Anda menggandakan kecepatan bit. Untuk membedakan antara bit, atau informasi, kecepatan dan kecepatan berbagai status sinyal diskrit, konsep kecepatan baud diperkenalkan. Baud adalah jumlah status sinyal diskrit yang berbeda per satuan waktu. Oleh karena itu, jika dua bit dikodekan dalam satu keadaan diskrit, laju bit adalah dua kali laju baud, yaitu 1 baud = 2 bps.

Jika kita memperhitungkan bahwa kabel kategori ke-5 dirancang untuk frekuensi 125 MHz, yaitu, mampu beroperasi pada baud rate 125 MBaud, maka kecepatan informasi pada satu pasangan terpilin akan menjadi 250 Mbps. Ingatlah bahwa ada empat pasangan terpilin dalam kabel, jadi jika Anda menggunakan keempat pasangan (Gbr. 14), maka Anda dapat meningkatkan kecepatan transmisi menjadi 250 Mbps4 = 1000 Mbps, yaitu, mencapai kecepatan yang diinginkan.

Seperti yang telah dicatat, ada lima level diskrit dalam pengkodean PAM-5, tetapi hanya empat level yang digunakan untuk mengirimkan dibit. Level kode redundan kelima (Forward Error Correction, FEC) digunakan untuk mekanisme konstruksi koreksi kesalahan. Ini diimplementasikan oleh encoder Trellis dan decoder Viterbi. Penggunaan mekanisme koreksi kesalahan memungkinkan untuk meningkatkan kekebalan kebisingan penerima sebesar 6 dB.

Pengkodean teralis

Mari kita pertimbangkan prinsip-prinsip pengkodean teralis berdasarkan encoder paling sederhana yang terdiri dari dua sel penyimpanan dan elemen XOR (Gbr. 15). Biarkan input dari encoder tersebut menerima urutan bit 0101110010 dengan kecepatan k bit/s. Jika sel pembacaan dipasang pada output encoder, beroperasi pada frekuensi dua kali frekuensi bit rate pada input encoder, maka laju aliran keluaran akan dua kali lebih tinggi dari laju aliran masukan. Dalam hal ini, sel pembacaan untuk paruh pertama siklus encoder membaca data pertama dari elemen logika XOR 2, dan paruh kedua siklus - dari elemen logika XOR 3. Akibatnya, setiap bit input diberikan dua bit keluaran, yaitu, dibit, bit pertama yang membentuk elemen XOR 2, dan yang kedua - elemen XOR 3. Dari diagram waktu keadaan encoder, mudah untuk melihat bahwa dengan urutan bit input 0101110010, urutan outputnya adalah 00 11 10 00 01 10 01 11 11 10.

Mari kita perhatikan satu fitur penting dari prinsip pembentukan dibit. Nilai setiap dibit yang dihasilkan tidak hanya bergantung pada bit informasi yang masuk, tetapi juga pada dua bit sebelumnya, yang nilainya disimpan dalam dua sel memori. Memang, jika diasumsikan bahwa A i adalah bit yang masuk, maka nilai elemen XOR 2 ditentukan oleh ekspresi , dan nilai elemen XOR 3 ditentukan oleh ekspresi . Jadi, dibit dibentuk dari sepasang bit, nilai yang pertama adalah , dan yang kedua adalah . Oleh karena itu, nilai dibit bergantung pada tiga keadaan: nilai bit input, nilai sel penyimpanan pertama, dan nilai sel penyimpanan kedua. Encoder semacam itu disebut encoder konvolusional tri-state (K = 3) dengan laju keluaran .

Lebih mudah untuk mempertimbangkan pekerjaan encoder berdasarkan bukan diagram waktu, tetapi yang disebut diagram keadaan. Keadaan encoder akan ditunjukkan menggunakan dua nilai - nilai sel penyimpanan pertama dan kedua. Misalnya, jika sel pertama menyimpan nilai 1 (Q1=1) dan sel kedua menyimpan 0 (Q2=0), maka status encoder dijelaskan dengan nilai 10. Ada empat status encoder yang berbeda: 00, 01, 10, dan 11.

Biarkan keadaan encoder sama dengan 00 di beberapa titik waktu Kami tertarik pada apa yang akan menjadi keadaan encoder pada titik waktu berikutnya dan berapa dibit yang akan dihasilkan dalam kasus ini. Ada dua kemungkinan hasil, tergantung pada bit mana yang masuk ke input encoder. Jika 0 diterima pada input encoder, maka keadaan encoder selanjutnya juga akan menjadi 00, tetapi jika 1 diterima, maka keadaan selanjutnya (yaitu setelah shift) akan menjadi 10. Nilai dibit yang dihasilkan dalam kasus ini dihitung menggunakan rumus dan . Jika input dari encoder adalah 0, maka dibit 00() akan dibangkitkan, jika inputnya 1, maka dibit 11() akan dibangkitkan. Lebih mudah untuk memvisualisasikan alasan di atas menggunakan diagram status (Gbr. 16), di mana status encoder ditunjukkan dalam lingkaran, dan bit yang masuk dan dibit yang dihasilkan ditulis dengan garis miring. Misalnya, jika bit yang masuk adalah 1, dan dibit yang dihasilkan adalah 11, maka kita menulis: 1/11.

Melanjutkan alasan serupa untuk semua kemungkinan status encoder lainnya, mudah untuk membuat diagram status lengkap, atas dasar nilai dibit yang dihasilkan oleh encoder dapat dengan mudah dihitung.

Dengan menggunakan diagram status encoder, mudah untuk membangun diagram waktu transisi untuk urutan bit input 0101110010 yang telah kita pertimbangkan.Untuk melakukan ini, sebuah tabel dibuat, kolom yang menunjukkan kemungkinan status encoder, dan baris menunjukkan titik waktu. Transisi yang mungkin antara keadaan encoder yang berbeda ditunjukkan oleh panah (berdasarkan diagram keadaan encoder lengkap - Gambar 17), di atas yang ditunjukkan bit input yang sesuai dengan transisi ini dan dibit yang sesuai. Misalnya, untuk dua kali pertama, diagram status encoder terlihat seperti yang ditunjukkan pada Gambar. delapan belas. Panah merah menunjukkan transisi yang sesuai dengan urutan bit yang dipertimbangkan.

Melanjutkan untuk menampilkan transisi yang mungkin dan nyata antara keadaan encoder yang berbeda, sesuai dengan titik waktu yang berbeda (Gbr. 19 , , ), kita memperoleh diagram pewaktuan lengkap dari status encoder (Gbr. 22).

Keuntungan utama dari metode pengkodean teralis di atas adalah kekebalan kebisingannya. Seperti yang akan ditunjukkan nanti, karena redundansi pengkodean (ingat bahwa setiap bit informasi diberi dibit, yaitu redundansi kode adalah 2), bahkan dalam kasus kesalahan penerimaan (misalnya, dibit 10 diterima secara keliru alih-alih dibit 11), urutan bit asli dapat dipulihkan.

Untuk mengembalikan urutan bit asli di sisi penerima, dekoder Viterbi digunakan.

Dekoder Viterbi

Dekoder Viterbi dalam hal penerimaan bebas kesalahan dari seluruh urutan dibit 00 11 10 00 01 10 01 11 11 10 akan memiliki informasi tentang urutan ini, serta tentang struktur enkoder (yaitu, tentang keadaannya diagram) dan tentang keadaan awalnya (00). Berdasarkan informasi ini, ia harus mengembalikan urutan bit asli. Mari kita pertimbangkan bagaimana pemulihan informasi asli terjadi.

Mengetahui keadaan awal encoder (00), serta kemungkinan perubahan dalam keadaan ini (00 dan 10), kami membuat diagram waktu untuk dua titik waktu pertama (Gbr. 22). Dalam diagram ini, hanya ada dua jalur yang mungkin dari keadaan 00, sesuai dengan dibit masukan yang berbeda. Karena dibit input dekoder adalah 00, maka, dengan menggunakan diagram status enkoder Trellis, kami menetapkan bahwa status enkoder berikutnya adalah 00, yang sesuai dengan bit awal 0.

Namun, kami tidak memiliki jaminan 100% bahwa dibit 00 yang diterima benar, jadi kami tidak boleh mengabaikan kemungkinan jalur kedua dari status 00 ke status 10, sesuai dengan dibit 11 dan bit asli 1. Dua jalur yang ditunjukkan pada diagramnya berbeda satu sama lain yang disebut error metric, yang untuk setiap jalurnya dihitung sebagai berikut. Untuk transisi yang sesuai dengan dibit yang diterima (yaitu, untuk transisi yang dianggap benar), metrik kesalahan diambil sama dengan nol, dan untuk transisi yang tersisa dihitung dari jumlah bit yang berbeda dalam dibit yang diterima dan dibit sesuai dengan transisi yang bersangkutan. Misalnya, jika dibit yang diterima adalah 00 dan dibit yang sesuai dengan transisi yang dimaksud adalah 11, maka metrik kesalahan untuk transisi tersebut adalah 2.

Untuk momen waktu berikutnya yang sesuai dengan dibit 11 yang diterima, dua status encoder awal akan dimungkinkan: 00 dan 10, dan akan ada empat status akhir: 00, 01, 10 dan 11 (Gbr. 23). Dengan demikian, untuk status akhir ini, ada beberapa kemungkinan jalur yang berbeda satu sama lain dalam metrik kesalahan. Saat menghitung metrik kesalahan, perlu untuk mempertimbangkan metrik status sebelumnya, yaitu, jika sebelumnya metrik untuk status 10 sama dengan 2, maka saat transisi dari status ini ke status 01, kesalahan metrik status baru (metrik seluruh jalur) akan menjadi sama dengan 2 + 1 = 3 .

Untuk momen waktu berikutnya yang sesuai dengan dibit 10 yang diterima, kami mencatat bahwa dua jalur mengarah ke status 00, 01 dan 11 (Gbr. 24). Dalam hal ini, perlu untuk meninggalkan hanya transisi yang sesuai dengan metrik kesalahan yang lebih kecil. Selain itu, karena transisi dari keadaan 11 ke keadaan 11 dan ke keadaan 01 dibuang, transisi dari keadaan 10 ke keadaan 11 yang sesuai dengan titik waktu sebelumnya tidak memiliki kelanjutan, oleh karena itu, juga dapat dibuang. Demikian pula, transisi yang sesuai dengan momen waktu sebelumnya dari keadaan 00 ke 00 dibuang.

Melanjutkan penalaran serupa, kita dapat menghitung metrik dari semua jalur yang mungkin dan menggambarkan semua jalur yang mungkin.

Pada saat yang sama, jumlah jalur yang mungkin itu sendiri ternyata tidak sebesar yang terlihat, karena kebanyakan dari mereka dibuang dalam proses konstruksi, karena tidak memiliki kelanjutan (Gbr. 25). Misalnya, pada siklus keenam dekoder, menurut algoritma yang dijelaskan, hanya empat jalur yang mungkin tersisa.

Demikian pula, pada siklus terakhir dekoder, hanya ada empat jalur yang mungkin (Gbr. 26), dan jalur sebenarnya, yang secara unik memulihkan urutan bit asli 0101110010, sesuai dengan metrik kesalahan yang sama dengan 0.

Saat menyusun diagram waktu yang dipertimbangkan, akan lebih mudah untuk menampilkan metrik kesalahan yang terakumulasi untuk berbagai status encoder dalam bentuk tabel. Tabel inilah yang merupakan sumber informasi atas dasar yang memungkinkan untuk mengembalikan urutan bit asli (Tabel 4).

Dalam kasus yang dijelaskan di atas, kami berasumsi bahwa semua dibit yang diterima oleh dekoder bebas dari kesalahan. Pertimbangkan lebih lanjut situasi ketika urutan dibit yang diterima mengandung dua kesalahan. Biarkan alih-alih urutan yang benar 00 11 10 00 01 10 01 11 11 10, decoder menerima urutan 00 11 11 00 11 10 01 11 11 10, di mana debit ketiga dan kelima salah. Mari kita coba menerapkan algoritma Viterbi yang dibahas di atas, berdasarkan pemilihan jalur dengan metrik kesalahan terkecil, ke urutan ini dan cari tahu apakah kita dapat memulihkan dalam cara yang benar urutan bit asli, yaitu, memperbaiki kesalahan buruk.

Hingga penerimaan dibit ketiga (gagal), algoritme untuk menghitung metrik kesalahan untuk semua transisi yang mungkin tidak berbeda dari kasus yang dipertimbangkan sebelumnya. Sampai titik ini, jalur yang ditandai pada Gambar 1 memiliki metrik kesalahan akumulasi terkecil. 27 merah. Setelah menerima dibit seperti itu, tidak ada lagi jalur dengan metrik kesalahan kumulatif sama dengan 0. Namun, dalam kasus ini, dua jalur alternatif dengan metrik sama dengan 1. Oleh karena itu, tidak mungkin untuk mengetahui pada tahap ini bit mana dari urutan asli yang sesuai dengan dibit yang diterima.

Situasi serupa akan muncul ketika menerima dibit kelima (juga salah) (Gbr. 28). Dalam hal ini, sudah akan ada tiga jalur dengan metrik yang sama dari akumulasi kesalahan, dan dimungkinkan untuk menetapkan jalur yang benar hanya ketika dibit berikut diterima.

Setelah menerima dibit kesepuluh, jumlah jalur yang mungkin dengan metrik akumulasi kesalahan yang berbeda akan menjadi cukup besar (Gbr. 29), namun, pada diagram di atas (menggunakan Tabel 5, yang menunjukkan metrik akumulasi kesalahan untuk berbagai jalur), tidak sulit untuk memilih satu-satunya jalur dengan metrik terkecil (pada Gambar 29

Contoh convolutional encoder yang dipertimbangkan hanya memiliki empat state yang berbeda: 00, 01, 10 dan 11. Teknologi 1000Base-T menggunakan convolutional encoder untuk delapan state yang berbeda (dengan tiga elemen delay), oleh karena itu disebut sebagai delapan posisi encoder . Selain itu, karena simbol ditransmisikan pada keempat pasang kabel yang dipilin secara bersamaan menggunakan penyandian PAM-5 lima tingkat, penyandian ini disebut 4D/PAM-5 empat dimensi.

Perbedaan signifikan lainnya dari encoder Trellis yang digunakan dalam teknologi 1000Base-T adalah algoritma transisi antara keadaan encoder yang berbeda. Dalam contoh paling sederhana kami, keadaan encoder pada saat berikutnya ditentukan hanya oleh keadaan saat ini dan bit input. Jadi jika Kondisi saat ini 00, dan bit input adalah 1, maka keadaan berikutnya, yaitu, bidang pergeseran bit dalam sel memori, akan sesuai dengan 10. Dalam encoder Trellis delapan posisi nyata, ada dua bit kontrol (input), dan transisi antara keadaan yang berbeda ditentukan oleh algoritma jarak terjauh antara titik-titik konstelasi sinyal. Sebagai berikut dari Gambar. 30 , encoder Trellis mengimplementasikan hubungan:

dimana d 6 , d 7 dan d 8 berturut-turut adalah bit data pada baris 6, 7 dan 8.

Mari kita jelaskan ini dengan contoh spesifik.

Ingatlah bahwa kode PAM-5 menggunakan lima level untuk pensinyalan: -2, -1, 0, +1, +2. Pada saat yang sama, level +2/–2 sesuai dengan tegangan +1/-1 V, dan level +1/-1 sesuai dengan tegangan +0,5/–0,5 V. Dengan mempertimbangkan bahwa empat sinyal level secara bersamaan ditransmisikan melalui empat pasangan bengkok dan masing-masing level ini dapat mengambil salah satu dari lima nilai, secara total kami mendapatkan 625 (5x5x5x5) kombinasi sinyal yang berbeda. Lebih mudah untuk menggambarkan berbagai kemungkinan keadaan sinyal pada apa yang disebut bidang sinyal. Pada bidang ini, setiap keadaan sinyal yang mungkin diwakili oleh titik sinyal, dan himpunan semua titik sinyal disebut konstelasi sinyal. Secara alami, tidak mungkin untuk menggambarkan ruang empat dimensi, oleh karena itu, untuk kejelasan, mari kita pertimbangkan konstelasi sinyal 5x5 dua dimensi. Konstelasi seperti itu secara formal dapat berkorespondensi dengan dua pasangan bengkok. Mari kita menggambar titik di sepanjang sumbu X yang sesuai dengan satu pasangan bengkok, dan di sepanjang sumbu Y - yang lain. Kemudian konstelasi 2D kita akan terlihat seperti yang ditunjukkan pada Gambar. 31 .

Perhatikan bahwa jarak minimum antara dua titik konstelasi tersebut adalah 1.

Di bawah pengaruh noise dan redaman sinyal, konstelasi sinyal mengalami distorsi (Gbr. 32), akibatnya posisi setiap titik sinyal menjadi kabur, dan jarak di antara mereka berkurang. Akibatnya, titik-titik dalam konstelasi sinyal menjadi sulit untuk dibedakan dan kemungkinan besar mereka akan bingung.

Oleh karena itu, salah satu tugas encoder Trellis adalah pembentukan konstelasi sinyal yang akan memberikan jarak maksimum antara titik sinyal yang berbeda. Untuk memahami bagaimana ini dilakukan, kami menyatakan level sinyal -1 dan +1 hingga X, dan level -2, 0, +2 hingga Y. Kemudian konstelasi awal dapat digambarkan seperti yang ditunjukkan pada Gambar. 33 .

Dengan membagi konstelasi ini menjadi dua subkonstelasi, salah satunya terbentuk dari titik XX dan YY, dan lainnya dari titik XY dan YX, dimungkinkan untuk meningkatkan jarak antara titik sinyal ke (Gbr. 34).

Saat menggunakan dua twisted pair, tugas encoder Trellis adalah mengirim hanya simbol milik salah satu konstelasi sinyal, misalnya, D0=XX+YY, lebih dari satu twisted pair, dan simbol milik konstelasi lain, misalnya D1 =XY+YX. Kemudian jarak antara simbol yang dikirim akan menjadi dua kali lebih besar dari pada konstelasi aslinya. Akibatnya, pengenalan titik-titik dalam konstelasi sinyal ditingkatkan, yaitu kekebalan kebisingan meningkat.

Encoder teralis nyata bekerja dengan cara yang kira-kira sama, menghasilkan simbol yang dikirim melalui empat pasangan bengkok, namun, karena setiap titik konstelasi sesuai dengan empat koordinat (satu untuk setiap pasangan) dan setiap titik dapat mengambil nilai X atau Y, maka ada 16 kombinasi berbeda untuk membentuk delapan sub-rasi bintang:

Dalam subkonstelasi yang dihasilkan, jarak minimum antar titik adalah dua kali lebih besar dari konstelasi aslinya. Selain itu, jarak minimum antara titik dua subkonstelasi yang berbeda juga sama dengan 2. Kedelapan konstelasi sinyal inilah yang membentuk diagram keadaan dari encoder Trellis. Misalnya, keadaan encoder 000 sesuai dengan kombinasi titik dari konstelasi D0D2D4D6 dalam arti bahwa titik dari konstelasi D0 ditransmisikan pada pasangan pertama, titik dari konstelasi D2 pada pasangan kedua, dan seterusnya. Kemungkinan keadaan encoder berikutnya akan sesuai dengan kombinasi seperti itu di mana jarak minimum antara simbol yang dikirim untuk setiap pasangan adalah 2.

Penggunaan pengkodean teralis sesuai dengan skema yang dijelaskan memungkinkan untuk mengurangi rasio signal-to-noise (SNR) sebesar 6 dB, yaitu, secara signifikan meningkatkan kekebalan kebisingan selama transmisi data.

KomputerTekan 2 "2002

Ini adalah kelanjutan dari artikel tentang pengkodean koreksi kesalahan, yang telah lama berada dalam konsep. Di bagian terakhir tidak ada yang menarik dari sudut pandang praktis - hanya informasi Umum tentang mengapa itu dibutuhkan, di mana itu diterapkan, dll. Bagian ini akan melihat beberapa (paling sederhana) kode untuk mendeteksi dan/atau mengoreksi kesalahan. Jadi ayo pergi.

Saya mencoba menggambarkan semuanya semudah mungkin untuk orang yang tidak pernah berurusan dengan informasi pengkodean, dan tanpa rumus matematika khusus.

Ketika kami mengirimkan pesan dari sumber ke penerima, kesalahan (gangguan, kerusakan peralatan, dll.) dapat terjadi selama transmisi data. Untuk mendeteksi dan memperbaiki kesalahan, digunakan pengkodean koreksi kesalahan, mis. menyandikan pesan sedemikian rupa sehingga pihak penerima mengetahui apakah telah terjadi kesalahan atau tidak, dan dapat memperbaiki kesalahan jika terjadi.

Padahal, pengkodean adalah penambahan informasi tambahan, verifikasi, ke informasi asli. Untuk pengkodean di sisi transmisi digunakan pembuat kode, dan di sisi penerima - gunakan dekoder untuk mendapatkan pesan asli.

Redundansi Kode adalah jumlah informasi verifikasi dalam pesan. Itu dihitung sesuai dengan rumus:

k/(i+k), di manaMisalnya, kami mengirimkan 3 bit dan menambahkan 1 bit cek - redundansinya adalah 1/(3+1) = 1/4 (25%).

k - jumlah bit cek,

i - jumlah bit informasi.

Kode paritas

Pengecekan paritas adalah metode yang sangat sederhana untuk mendeteksi kesalahan dalam paket data yang dikirimkan. Dengan kode ini, kami tidak dapat memulihkan data, tetapi kami hanya dapat mendeteksi satu kesalahan.Setiap paket data berisi: satu bit paritas, atau yang disebut sedikit paritas. Bit ini diset saat data ditulis (atau dikirim), kemudian dihitung dan dibandingkan saat data dibaca (diterima). Dia sama dengan jumlah modulo 2 semua bit data dalam paket. Itu adalah jumlah 1 dalam satu batch akan selalu genap. Mengubah bit ini (misalnya dari 0 ke 1) melaporkan kesalahan.

Diagram blok encoder untuk kode ini ditunjukkan di bawah ini.

dan dan dekoder

Contoh:

Data awal: 1111

0 (1 + 1 + 1 + 1 = 0 (mod 2))

Data yang diterima: 1 0 110 (bit kedua diubah)

Seperti yang kita lihat, jumlah unit dalam paket yang diterima ganjil, oleh karena itu, terjadi kesalahan selama transmisi.

Seperti disebutkan sebelumnya, metode ini hanya berfungsi untuk menentukan satu kesalahan. Dalam kasus perubahan keadaan dua bit, ada kemungkinan bahwa perhitungan bit kontrol akan bertepatan dengan yang tertulis. Dalam hal ini, sistem tidak akan mendeteksi kesalahan, yang tidak baik. Sebagai contoh:

Data awal: 1111

Data setelah penyandian: 1111 0 (1 + 1 + 1 + 1 = 0 (mod 2))

Data yang diterima: 1 00 10 (bit 2 dan 3 berubah)

Jumlah yang ada dalam data yang diterima genap, dan oleh karena itu dekoder tidak akan mendeteksi kesalahan.

Karena sekitar 90% dari semua kesalahan tidak beraturan terjadi dengan satu digit, bahkan paritas cukup untuk sebagian besar situasi.

Kode Hamming

Seperti disebutkan di bagian sebelumnya, Richard Hamming melakukan banyak hal untuk pengkodean koreksi kesalahan. Secara khusus, ia telah mengembangkan kode yang mendeteksi dan mengoreksi kesalahan tunggal dengan bit pemeriksaan tambahan sesedikit mungkin. Untuk setiap jumlah karakter cek, tanda khusus formulir (k, i) digunakan, di mana k adalah jumlah karakter dalam pesan, i adalah jumlah karakter informasi dalam pesan. Misalnya ada kode (7, 4), (15, 11), (31, 26). Setiap simbol cek dalam kode Hamming mewakili jumlah modulo 2 dari beberapa data berikutnya. Mari kita lihat contoh segera, ketika jumlah bit informasi i di blok adalah 4 - ini adalah kode (7,4), jumlah karakter centang adalah 3. Secara klasik, karakter ini terletak di posisi yang sama dengan kekuatan dari dua dalam urutan menaik:cek bit pertama pada 2 0 = 1;

cek kedua bit pada 2 1 = 2;

cek bit ketiga pada 2 2 = 4;

tetapi Anda juga dapat menempatkannya di akhir blok data yang ditransmisikan (tetapi kemudian rumus untuk menghitungnya akan berbeda).

Sekarang mari kita hitung simbol cek ini:

r1 = i1 + i2 + i4

r2 = i1 + i3 + i4

r3 = i2 + i3 + i4

Jadi, dalam pesan yang disandikan, kami mendapatkan yang berikut:

r1 r2 i1 r3 i2 i3 i4

Pada prinsipnya, operasi algoritma ini dianalisis dengan sangat rinci dalam artikel Kode Hamming. Contoh pengoperasian algoritma, jadi saya tidak melihat gunanya menjelaskan secara rinci dalam artikel ini. Sebagai gantinya, saya akan memberikan diagram blok encoder:

dan dekoder

(mungkin cukup membingungkan, tetapi tidak berhasil lebih baik)

E0,e1,e2 didefinisikan sebagai fungsi tergantung pada bit k1 - k7 yang diterima oleh decoder:

e0 = k1 + k3 + k5 + k7 mod 2

e1 = k2 + k3 + k6 + k7 mod 2

e2 = k4 + k5 + k6 + k7 mod 2

Himpunan nilai-nilai ini e2e1e0 ada catatan biner dari posisi di mana kesalahan terjadi saat mengirimkan data. Dekoder menghitung nilai-nilai ini, dan jika tidak semuanya sama 0 (yaitu, itu tidak akan berfungsi 000), lalu perbaiki kesalahannya.

Kode-karya

Dalam saluran komunikasi, selain kesalahan tunggal yang disebabkan oleh noise, sering juga terjadi kesalahan burst yang disebabkan oleh noise impuls, fading, atau putus-putus (selama perekaman video digital). Dalam hal ini, ratusan, atau bahkan ribuan bit informasi berturut-turut terpengaruh. Jelas bahwa tidak ada kode koreksi kesalahan yang dapat mengatasi kesalahan seperti itu. Untuk mengatasi kesalahan tersebut, digunakan kode produk. Prinsip operasi kode semacam itu ditunjukkan pada gambar:

Informasi yang dikirimkan dikodekan dua kali: di encoder eksternal dan internal. Buffer dipasang di antara mereka, yang operasinya ditunjukkan pada gambar:

Kata-kata informasi melewati encoder koreksi kesalahan pertama, yang disebut eksternal, karena itu dan dekoder yang sesuai terletak di tepi sistem pengkodean koreksi kesalahan. Di sini, periksa karakter yang ditambahkan padanya, dan mereka, pada gilirannya, dimasukkan ke dalam buffer kolom demi kolom, dan output baris demi baris. Proses ini disebut percampuran atau menyisipkan.

Ketika string dikeluarkan dari buffer, periksa karakter kode internal yang ditambahkan ke dalamnya. Dalam urutan ini, informasi ditransmisikan melalui saluran komunikasi atau direkam di suatu tempat. Mari kita sepakat bahwa kode dalam dan luar adalah kode Hamming dengan tiga simbol centang, yaitu keduanya dapat memperbaiki satu kesalahan dalam kata sandi(jumlah "kubus" pada gambar tidak kritis - itu hanya diagram). Di sisi penerima, ada susunan memori (buffer) yang sama persis, di mana informasi dimasukkan baris demi baris, dan output kolom demi kolom. Ketika terjadi kesalahan burst (melintasi gambar di baris ketiga dan keempat), itu didistribusikan dalam porsi kecil dalam kata-kata kode dari kode luar dan dapat diperbaiki.

Tujuan dari kode eksternal jelas - memperbaiki kesalahan batch. Mengapa kita membutuhkan kode internal? Gambar, selain batch satu, menunjukkan satu kesalahan (kolom keempat, garis atas). Ada dua kesalahan dalam kata kode yang terletak di kolom keempat, dan itu tidak dapat diperbaiki, karena kode luar dirancang untuk memperbaiki satu kesalahan. Untuk keluar dari situasi ini, hanya kode internal yang diperlukan, yang akan memperbaiki kesalahan tunggal ini. Data yang diterima pertama-tama melewati dekoder internal, di mana kesalahan tunggal dikoreksi, kemudian ditulis ke buffer baris demi baris, output dalam kolom dan diumpankan ke dekoder eksternal, di mana kesalahan burst diperbaiki.

Penggunaan kode produk sangat meningkatkan kekuatan kode koreksi kesalahan dengan penambahan sedikit redundansi.

P.S.: Saya mengerjakan topik ini dengan cermat 3 tahun yang lalu, ketika saya sedang menulis proyek kelulusan saya, mungkin saya melewatkan sesuatu. Semua koreksi, komentar, keinginan - silakan melalui pesan pribadi

Pengkodean pada dua saluran yang lebih rendah mencirikan metode penyajian informasi dengan sinyal yang merambat melalui media transportasi. Pengkodean dapat dianggap sebagai dua tahap. Dan jelas bahwa decoding simetris diimplementasikan di sisi penerima.

Pengkodean logika data mengubah aliran bit dari bingkai lapisan MAC yang dihasilkan menjadi urutan simbol yang akan dikodekan secara fisik untuk transportasi melalui saluran komunikasi. Skema yang berbeda digunakan untuk pengkodean logis:

- 4B / 5B - setiap 4 bit aliran input dikodekan dengan karakter 5-bit (Tabel 1.1). Ternyata redundansi ganda, karena 2 4 = 16 kombinasi input ditunjukkan oleh simbol dari 2 5 = 32. Biaya untuk jumlah interval bit adalah: (5-4) / 4 = 1/4 (25%). Redundansi ini memungkinkan Anda untuk menentukan sejumlah simbol layanan yang berfungsi untuk sinkronisasi. Digunakan di 100BaseFX/TX, FDDI

- 8B / 10B - skema serupa (8 bit dikodekan dengan simbol 10-bit) tetapi redundansi sudah 4 kali (256 input dalam 1024 output).

- 5B/6B - 5 bit aliran input dikodekan dengan karakter 6-bit. Digunakan di 100VG-AnyLAN

- 8B/6T - 8 bit aliran input dikodekan dengan enam digit ternary (T = ternary) (-,0,+). Misalnya: 00j: +-00+-; 01 jam: 0+-+=0; Kode memiliki redundansi 3 6/2 8 = 729/256 = 2,85. Kecepatan pengangkutan simbol ke saluran lebih rendah dari kecepatan bit dan penerimaannya untuk penyandian. Digunakan di 100BaseT4.

- Penyisipan bit - skema seperti itu berfungsi untuk mengecualikan urutan bit yang tidak valid. Kami akan menjelaskan pekerjaannya pada implementasi dalam protokol HDLC. Di sini aliran input terlihat seperti urutan bit yang berkesinambungan, dengan rantai lebih dari lima yang berdekatan 1 diuraikan sebagai sinyal layanan (contoh: 01111110 adalah bendera pembatas bingkai). Jika aliran siaran berisi urutan kontinu dari 1 , kemudian setelah setiap kelima dalam aliran keluaran, pemancar menyisipkan 0 . Penerima menganalisis rantai masuk, dan jika setelah rantai 011111 Ia melihat 0 , lalu membuangnya dan urutannya 011111 menambahkan ke sisa aliran data output. Jika sedikit diterima 1 , maka urutannya 011111 terlihat seperti simbol layanan. Teknik ini memecahkan dua masalah - untuk mengecualikan urutan monoton panjang yang tidak nyaman untuk sinkronisasi otomatis pengkodean fisik dan memungkinkan pengenalan batas bingkai dan status khusus dalam aliran bit berkelanjutan.

Tabel 1 - Pengodean 4V / 5V

| karakter masukan | Simbol keluaran |

|---|---|

| 0000 (0) | 11110 |

| 0001 (1) | 01001 |

| 0010 (2) | 10100 |

| 0011 (3) | 10101 |

| 0100 (4) | 01010 |

| 0101 (5) | 01011 |

| 0110 (6) | 01110 |

| 0111 (7) | 01111 |

| 1000 (8) | 10010 |

| 1001 (9) | 10011 |

| 1010(A) | 10110 |

| 1011(B) | 10111 |

| 1100 (C) | 11010 |

| 1101 (D) | 11011 |

| 1110(E) | 11100 |

| 1111 (P) | 11101 |

Redundansi pengkodean logis memungkinkan untuk memfasilitasi tugas pengkodean fisik - untuk menghilangkan urutan bit yang tidak nyaman, meningkatkan karakteristik spektral dari sinyal fisik, dll. Pengkodean fisik/sinyal menulis aturan untuk mewakili karakter diskrit, hasil pengkodean logis menjadi hasil sinyal garis fisik. Sinyal fisik dapat memiliki bentuk kontinu (analog) - jumlah nilai yang tak terbatas, dari mana satu set valid yang dapat dikenali dipilih. Di tingkat sinyal fisik alih-alih bit rate (bps) gunakan konsep tingkat perubahan sinyal garis yang diukur dalam baud. Definisi ini mendefinisikan jumlah perubahan dalam berbagai keadaan garis per satuan waktu. Pada tingkat fisik, sinkronisasi penerima dan pemancar. Sinkronisasi eksternal tidak digunakan karena tingginya biaya implementasi saluran lain. Banyak skema pengkodean fisik yang menyinkronkan sendiri — mereka memungkinkan sinyal clock diekstraksi dari urutan status saluran yang diterima.

Berebut pada tingkat fisik, ini memungkinkan Anda untuk menekan karakteristik spektral sinyal yang sangat kuat, mengolesi mereka melalui pita spektrum tertentu. Interferensi yang sangat kuat mendistorsi saluran transmisi yang berdekatan. Saat berbicara tentang pengkodean fisik, istilah berikut dapat digunakan:

- Pengkodean transisi - informatif adalah transisi dari satu keadaan ke keadaan lain

- Pengkodean potensial - informatif adalah tingkat sinyal pada titik waktu tertentu

- Polar - sinyal dari satu polaritas diimplementasikan untuk mewakili satu nilai, sinyal dari polaritas lain untuk mewakili yang lain. Dalam transportasi serat optik, amplitudo pulsa digunakan sebagai pengganti polaritas

- Unipolar - sinyal dari satu polaritas diimplementasikan untuk mewakili satu nilai, sinyal nol - untuk yang lain

- Bipolar - menggunakan negatif, positif, dan nol untuk mewakili tiga keadaan

- Biphasic - di setiap interval bit ada transisi dari satu keadaan ke keadaan lain, yang digunakan untuk menyorot sinyal jam.

Skema pengkodean populer yang digunakan di jaringan lokal

AMI/ABP

AMI - Alternate Mark Inversion atau ABP - Alternate bipolare, skema bipolar yang menggunakan nilai +V, 0V dan -V. Semua bit nol memiliki nilai 0V, bit tunggal memiliki nilai bolak-balik +V, -V (Gbr. 1). Digunakan di DSx (DS1 - DS4), ISDN. Skema seperti itu tidak sepenuhnya menyinkronkan sendiri - rantai nol yang panjang akan menyebabkan hilangnya sinkronisasi.

Gambar 1

MAMI - Modified Alternate Mark Inversion, atau ASI - sirkuit AMI yang dimodifikasi, pulsa polaritas bolak-balik dikodekan oleh 0, dan 1 dengan potensi nol. Digunakan dalam ISDN (S/T - antarmuka).

B8ZS - Bipolar dengan 8 Substitusi Nol, skema yang mirip dengan AMI, tetapi mengecualikan rantai 8 atau lebih nol untuk sinkronisasi (karena penyisipan bit).

HDB3 - High Density Bipolar 3, skema yang mirip dengan AMI, tetapi tidak memungkinkan transmisi rantai lebih dari tiga nol. Alih-alih urutan empat nol, salah satu dari empat kode bipolar dimasukkan. (Gbr.2)

Menggambar - 2

Menggambar - 2

Pengkodean Manchester

Pengkodean Manchester adalah pengkodean sinkronisasi mandiri polar/unipolar dua fase. Bit saat ini dikenali oleh arah perubahan status di tengah interval bit: dari -V ke +V: 1. Dari +V ke -V: 0. Mungkin tidak ada transisi di awal interval . Digunakan dalam Ethernet. (Dalam versi awal - unipolar). (gbr.3)

Menggambar - 3

Menggambar - 3

Pengkodean manchester diferensial - kode sinkronisasi mandiri polar / unipolar dua fase. Bit saat ini dikenali dengan adanya transisi pada awal interval bit (Gbr. 4.1), misalnya, 0 - ada transisi (Fragmen vertikal), 1 - tidak ada transisi (Fragmen horizontal). Anda dapat, dan sebaliknya, menentukan 0 dan 1. Selalu ada transisi di tengah interval bit. Ini diperlukan untuk sinkronisasi. Token Ring menggunakan versi modifikasi dari skema ini, dimana selain bit 0 dan 1, dua bit j dan k juga didefinisikan (Gbr. 4.2). Tidak ada transisi di tengah interval. Bit K memiliki transisi pada awal interval, tetapi j tidak.

Gambar - 4.1 dan 4.2

Gambar - 4.1 dan 4.2

Pengkodean tiga tingkat dengan pengacakan yang tidak menyinkronkan sendiri. Level (+V, 0, -V) digunakan konstan pada baris setiap interval bit. Saat mentransfer 0, nilainya tidak berubah, saat mentransfer 1, mereka berubah menjadi yang berdekatan dalam rantai +V, 0, -V, 0, +V, dan seterusnya. (Gbr. 5). Skema semacam itu adalah versi NRZI yang rumit. Digunakan dalam FDDI dan 100BaseTX.

Menggambar - 5

Menggambar - 5

NRZ dan NRZI

NRZ - Tidak kembali ke nol (tanpa kembali ke nol), sirkuit non-transitif bipolar (menyatakan perubahan di perbatasan), yang memiliki 2 opsi. Opsi pertama adalah status NRZ non-diferensial (digunakan dalam RS-232) yang secara langsung mencerminkan nilai bit (Gbr. 6.a). Dalam versi lain - diferensial, status NRZ berubah pada awal interval bit untuk 1 dan tidak berubah untuk 0. (Gbr. 6.B). Tidak ada pengikatan 1 dan 0 pada keadaan tertentu.

NRZI - Tidak kembali ke nol Sirkuit NRZ yang dimodifikasi dan terbalik (Gbr. 6.c). Di sini keadaan dibalik pada awal interval bit 0, dan tidak berubah ketika ditransmisikan 1. Skema representasi terbalik juga dimungkinkan. Digunakan di FDDI, 100BaseFX.

Gambar - 6-a, b, c

Gambar - 6-a, b, c

RZ - Kembali ke nol (dengan kembali ke nol), sirkuit sinkronisasi mandiri transitif bipolar. Negara dalam momen tertentu interval bit selalu kembali ke nol. Memiliki opsi diferensial/non-diferensial. Dalam diferensial, tidak ada pengikatan 1 dan 0 ke keadaan. (Gbr. 7.a).

Gambar - 7-a, b

Gambar - 7-a, b

FM 0 - Modulasi Frekuensi 0 (modulasi frekuensi), menyinkronkan sendiri kode kutub. Membalik pada batas setiap interval bit. Ketika 1 ditransmisikan selama interval bit, keadaan tidak berubah. Saat mentransmisikan 0, keadaan dibalik di tengah interval bit. (Gbr. 8). Digunakan di LocalTalk.

Menggambar - 8

Menggambar - 8

PAM 5 - Modulasi Amplitudo Pulsa, pengkodean bipolar lima tingkat, di mana sepasang bit, tergantung pada sejarahnya, ternyata menjadi salah satu dari 5 level potensial. Membutuhkan bandwidth yang sempit (setengah bit rate). Digunakan dalam 1000BaseT.

Di sini, sepasang bit ternyata menjadi satu simbol Kuarter (simbol Kuarter-nary), di mana masing-masing sesuai dengan salah satu dari 4 level sinyal. Tabel menunjukkan representasi karakter dalam jaringan ISDN.

4B3T - blok 4 bit (16 status) dikodekan dengan tiga simbol ternary (27 simbol). Dari banyak kemungkinan metode perubahan, pertimbangkan MMS43, yang digunakan dalam antarmuka BRI jaringan ISDN (tabel). Terapkan di sini metode khusus untuk menghilangkan komponen konstan tegangan di saluran, akibatnya pengkodean sejumlah kombinasi tergantung pada prasejarah - keadaan di mana pembuat enkode berada. Contoh: urutan bit 1100 1101 akan direpresentasikan sebagai: + + + - 0 -.

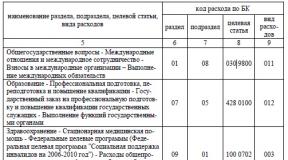

| Kode biner | S1 | Transisi | S2 | Transisi | S3 | Transisi | S4 | Transisi |

|---|---|---|---|---|---|---|---|---|

| 0001 | 0 — + | S1 | 0 — + | S2 | 0 — + | S3 | 0 — + | S4 |

| 0111 | — 0 + | S1 | — 0 + | S2 | — 0 + | S3 | — 0 + | S4 |

| 0100 | — + 0 | S1 | — + 0 | S2 | — + 0 | S3 | — + 0 | S4 |

| 0010 | + — 0 | S1 | + — 0 | S2 | + — 0 | S3 | + — 0 | S4 |

| 1011 | + 0 — | S1 | + 0 — | S2 | + 0 — | S3 | + 0 — | S4 |

| 1110 | 0 + — | S1 | 0 + — | S2 | 0 + — | S3 | 0 + — | S4 |

| 1001 | + — + | S2 | + — + | S3 | + — + | S4 | — — — | S1 |

| 0011 | 0 0 + | S2 | 0 0 + | S3 | 0 0 + | S4 | — — 0 | S2 |

| 1101 | 0 + 0 | S2 | 0 + 0 | S3 | 0 + 0 | S4 | — 0 — | S2 |

| 1000 | + 0 0 | S2 | + 0 0 | S3 | + 0 0 | S4 | 0 — — | S2 |

| 0110 | — + + | S2 | — + + | S3 | — — + | S2 | — — + | S3 |

| 1010 | + + — | S2 | + + — | S3 | + — — | S2 | + — — | S3 |

| 1111 | + + 0 | S3 | 0 0 — | S1 | 0 0 — | S1 | 0 0 — | S3 |

| 0000 | + 0 + | S3 | 0 — 0 | S1 | 0 — 0 | S2 | 0 — 0 | S3 |

| 0101 | 0 + + | S3 | — 0 0 | S1 | — 0 0 | S2 | — 0 0 | S3 |

| 1100 | + + + | S4 | — + — | S1 | — + — | S2 | — + — | S3 |

Hasil

Skema yang tidak menyinkronkan sendiri, bersama dengan pengkodean logis dan definisi panjang interval bit yang tetap, memungkinkan sinkronisasi tercapai. Bit awal dan bit berhenti berfungsi untuk sinkronisasi, dan bit pemeriksaan memperkenalkan redundansi untuk meningkatkan keandalan penerimaan.

frekuensi diskrit, yang menghasilkan kebisingan EMI yang signifikan. Dalam hal sistem dengan kabel tanpa pelindung dan transmisi frekuensi tinggi 2,5 Gbps, kebisingan EMI mencapai tingkat yang signifikan. Perebutan membuat daya terpancar dari saluran komunikasi terlihat seperti white noise. Ini membantu memenuhi persyaratan EMC.

Pengacak, lihat gbr. 2.5.14., diimplementasikan pada register geser 16-bit dengan masukan(LFSR) yang mengimplementasikan polinomial

G(x) = X16 + X5 + X4 + X3 +1

register 16 bit | ||||||||||||||||||||||||||||||||||||||||||

pergeseran mundur | ||||||||||||||||||||||||||||||||||||||||||

komunikasi (LFSR), | ||||||||||||||||||||||||||||||||||||||||||

mewujudkan polinomial | ||||||||||||||||||||||||||||||||||||||||||

G(x) = X16 + X5 + X4 + X3 +1 | X 1X 2 | X 7X 8 | X9X10 | X 13X 14 | ||||||||||||||||||||||||||||||||||||||

register geser | ||||||||||||||||||||||||||||||||||||||||||

byte Scr(k:k+7) | ||||||||||||||||||||||||||||||||||||||||||

register penyangga | ||||||||||||||||||||||||||||||||||||||||||

byte Scr(k:k+7) | ||||||||||||||||||||||||||||||||||||||||||

diacak | ||||||||||||||||||||||||||||||||||||||||||

byte (A'B'C'D'E'F'G'H') | ||||||||||||||||||||||||||||||||||||||||||

Gambar 2.5.14. pengacak

Beberapa aturan untuk menerapkan pengacak

1. Dalam implementasi multi-line link, pengacak yang terkait dengan setiap baris harus bekerja sama, mempertahankan nilai yang sama secara bersamaan di semua LFSR.

2. Pengacakan diterapkan pada karakter 'D' yang membentuk paket TLP(DLL) dan DLLP, termasuk urutan tunggu logis (00h). Karakter 'D' dalam kumpulan perintah TS1 dan TS2 tidak diacak.

3. Karakter 'K' dan karakter dalam set perintah seperti TS1, TS2, SKIP, FTS, dan tunggu listrik tidak diacak. Karakter-karakter ini melewati logika pengacakan.

4. Karakter yang terkait dengan urutan yang cocok tidak diacak.

5. Ketika karakter COM keluar dari pengacak (COM tidak diacak) ia menginisialisasi LFSR. Nilai yang diinisialisasi LFSR 16-bit sama dengan FFFFh. Dengan cara yang sama, di sisi penerima, ketika karakter COM memasuki descrambler, itu diinisialisasi.

6. Dengan satu pengecualian, LFSR maju delapan kali berturut-turut untuk mengirimkan setiap karakter (karakter D atau K). LFSR tidak maju pada tanda SKP yang dimiliki oleh set perintah SKIP. Alasan untuk ini adalah penerima paket yang masuk dapat menambah atau menghapus simbol SKP untuk menyesuaikan jam. Perubahan jumlah karakter di penerima dibandingkan dengan jumlah karakter yang dikirimkan akan mengakibatkan hilangnya sinkronisasi antara nilai LFSR penerima dan pemancar.

Setelah pengacakan, karakter 8-bit (8b karakter) dikodekan menjadi karakter 10-bit (10b karakter) menggunakan logika encoder 8b/10b. Ada, tentu saja, kerugian 25% dalam bit rate nyata karena perluasan setiap karakter 8b menjadi karakter 10b. Karakter didefinisikan sebagai byte 8-bit unencoded dari paket. Sebuah karakter 8-bit dipasok ke encoder 8b/10b bersama dengan sinyal yang menunjukkan apakah itu karakter data (D) atau karakter kontrol (K). Sebuah karakter didefinisikan sebagai ekuivalen 10-bit yang dikodekan dari 8- sedikit karakter. Tujuan utama 8b/10b

pengkodean karakter paket adalah untuk membuat densitas yang cukup dari transisi 1-ke-0 dan 0-ke-1 dalam bitstream karakter sehingga

penerima dapat mengekstrak sinyal sinkronisasi dari aliran simbol menggunakan

loop terkunci fase (PLL) dan dengan demikian memecahkan masalah sinkronisasi bit dari aliran simbol pada input penerima dan masalah sinkronisasi bingkai dari paket-paket yang masuk. Perhatikan bahwa sinyal clock yang digunakan untuk menyinkronkan aliran bit serial pada keluaran pemancar tidak ditransmisikan secara terpisah melalui tautan komunikasi. Untuk menyinkronkan paket yang masuk, sinyal clock digunakan, yang dialokasikan oleh penerima menggunakan loop fase-terkunci.

Logika pengkodean 8b/10b ditemukan oleh IBM pada tahun 1982 dan dijelaskan dalam ANSI X3.230-1994, Pasal 11 (dan juga IEEE 802.3z, 36.2.4) dan Paten AS 4.486.739, berjudul "Byte Oriented DC Balanced 8b/10b Kode Transmisi Blok Dipartisi".

Berikut ini adalah manfaat dari pengkodean 8b/10b:

- sinyal jam bawaan;

- keseimbangan DC;

- pengkodean karakter kontrol khusus;

- deteksi kesalahan.

Kerugian dari pengkodean 8b/10b adalah karena perluasan setiap karakter 8-bit menjadi simbol 10-bit sebelum transmisi, laju transmisi aktual berkurang 25%.

Properti karakter 10-bit (10b)

Saat mentransmisikan karakter 10-bit, jumlah rata-rata 1 yang ditransmisikan selama periode waktu sama dengan jumlah 0 yang ditransmisikan, terlepas dari karakter 8-bit mana yang ditransmisikan, yaitu, transmisi karakter adalah DC seimbang.

- Bitstream karakter 10-bit tidak pernah berisi lebih dari lima 1 atau 0 berturut-turut.

Setiap karakter 10-bit berisi empat 0 dan enam 1 (tidak harus bersebelahan), atau enam 0 dan empat 1 (tidak harus bersebelahan), atau lima 0 dan lima 1 (tidak harus bersebelahan).

Setiap karakter 10-bit dibagi menjadi dua blok: yang pertama panjangnya enam bit dan yang kedua panjangnya empat bit. Tidak ada lebih dari empat 1 atau empat 0 dalam blok 6-bit. Tidak ada lebih dari tiga 1 atau tiga 0 dalam blok 4-bit.

- Simbol apa pun yang tidak memiliki properti yang dijelaskan di atas dianggap sebagai kesalahan dan penerusnya melaporkan kesalahan.

konsep ketidaksetaraan karakter mengacu pada perbedaan antara jumlah satu dan nol dalam karakter 10-bit. Bila jumlah angka nol pada suatu simbol lebih besar dari jumlah angkanya, maka ketidaksetaraan negatif(misalnya 0101000101b).

Ketika ada lebih 1s dalam simbol dari 0s, itu adalah pertidaksamaan positif(misalnya, 1001101110b). Ketika sebuah simbol memiliki angka 1s dan 0s yang sama, itu adalah ketidaksetaraan netral(misalnya 0110100101b).

Setiap karakter 10-bit berisi salah satu dari angka nol dan satu berikut (tidak harus berurutan):

- empat 0 dan enam 1 (+ pertidaksamaan);

- enam 0 dan empat 1 (- ketidaksetaraan);

- lima 0 dan lima 1 (ketidaksamaan netral)

Encoder keluaran menghasilkan karakter 10-bit yang setara bersama dengan

pemeriksaan paritas saat ini(Disparitas Berjalan Saat Ini, CRD), atau ketidaksetaraan simbol saat ini(Disparitas Berjalan Saat Ini, CRD), yang mencerminkan keseimbangan jumlah total satu dan nol yang ditransmisikan melalui saluran sejak inisialisasi, dan memiliki karakteristik sebagai berikut:

Keadaan CRD saat ini mencerminkan keseimbangan 1s dan 0s yang ditransmisikan sejak saluran diinisialisasi;

- keadaan awal CRD (sebelum transmisi data) bisa positif (+) atau negatif ( –);

- keadaan CRD saat ini bisa positif (+) jika lebih dari nol dikirim, atau negatif(-) jika lebih banyak nol dari satu yang dilewati;

- setiap karakter diubah sesuai dengan tabel, dengan mempertimbangkan keadaan saat ini

- setelah karakter terakhir dikodekan, CRD tetap sama jika dihasilkan karakter 10 bit memiliki ketidaksetaraan netral(n), atau berubah ke polaritas yang berlawanan jika simbol yang dihasilkan memiliki positif (+) atau negatif(–) ketidaksetaraan .

Prosedur pengkodean 8b/10b

Pengkodean dilakukan dengan melihat dua pasang tabel (satu pasang untuk pengkodean karakter data, pasangan lainnya untuk penyandian karakter perintah), Gbr.2.5.15. Pilihan pasangan tabel ditentukan oleh nilai D/K tanda. Untuk data dan tanda perintah, bit karakter ABCDE yang dikodekan yang masuk ke input encoder dari pengacak, dengan mempertimbangkan nilai CRD yang dihitung dari hasil pengkodean karakter sebelumnya, tentukan nilai bit abcdei bagian karakter dari tabel yang sesuai (pengkodean tabel 5b / 6b) . Untuk tanda data dan tanda perintah, bit dari tanda yang dikodekan FGH yang masuk ke input encoder dari pengacak, dengan mempertimbangkan nilai CRD yang dihitung dari hasil pengkodean bagian abcdei tanda sebelumnya, ditentukan dari tabel yang sesuai nilai bit fghj dari bagian simbol (Tabel 3b/4b coding). Himpunan bit abcdeifghj membentuk simbol tanda D/K

ABCD EFGH. Himpunan bit abcdeifghj juga menghitung ketidaksetaraan simbol saat ini, yang pada gilirannya menentukan nilai CRD untuk pengkodean karakter berikutnya.

Byte dari pengacak | |||||||||||||||

8b tanda saat ini | |||||||||||||||

Tabel 5b/6b coding

untuk tanda data

pengkodean untuk karakter perintah

arti masa depan | ||||||||||||||||||

definisi karakter | ||||||||||||||||||

Paralel-sekuensial | ||||||||||||||||||

transformasi yang solid | ||||||||||||||||||

Aliran serial di-clock oleh jam Tx

Beras. 2.5.15. Prosedur pengkodean 8b/10b

1. Untuk kenyamanan notasi, tanda data dan tanda perintah dari bentuk biner

- bit dalam tanda dilambangkan huruf kapital A sampai H;

- tanda dibagi menjadi dua blok, tanda pertama panjangnya 3 bit (paling signifikan) dan tanda kedua panjangnya 5 bit (yang lebih rendah);

- blok dicerminkan;

- tanda mengambil bentuk Zxx.y, di mana:

Z - D atau K untuk data atau karakter kontrol

xx - nilai desimal bidang 5 bit

pada - nilai desimal bidang 3-bit

Tanda 6Ah dipilih misalnya pada gambar. 2.5.16. | muncul sebagai D10.3 |

||||||

dalam tabel konversi 8b/10b | |||||||

penunjukan 8b | Contoh data |

||||||

Permutasi | |||||

subblok | |||||

Nilai desimal | |||||

subblok | |||||

terakhir | |||||

Beras. 2.5.16. Algoritma untuk mengubah karakter dari bentuk biner ke bentuk nama karakter.

2. Jika ketidaksetaraan saat ini dari karakter sebelumnya adalah positif (CRD +), maka saat mengkodekan blok EDCBA 5-bit dari Tabel. 2.5.14. (untuk tanda

data) dan dari Tabel. 2.5.15.(untuk tanda perintah) bit abcdei dipilih. sesuai dengan nilai CRD- saat ini.

tab. 2.5.14.. Encoding 5-bit hingga 6-bit untuk karakter data

Nama byte | Tidak berkode | RD saat ini - | RD+ . saat ini |

bit EDCBA | |||

Jika ketidaksetaraan saat ini dari karakter sebelumnya adalah negatif (CRD -), maka saat menyandikan blok EDCBA 5-bit dari Tabel. 2.5.14. (untuk tanda

data) dan dari Tabel. 2.5.15. (untuk tanda perintah) bit abcdei dipilih. sesuai dengan nilai CRD + .I.e. saat mengkodekan blok EDCBA 5-bit, nilai CRD dibalik.

tab. 2.5.15. Pengkodean 5 bit hingga 6 bit untuk karakter kontrol

Nama byte | Tidak berkode | RD saat ini - | RD+ . saat ini |

bit EDCBA | |||

3. Ketidaksetaraan dihitung untuk urutan bit abcdei. Itu bisa mengambil nilai: positif, negatif atau netral.

4. Jika nilai pertidaksamaan yang dihitung adalah positif atau negatif (+ atau-), lalu saat menyandikan blok HGF 3-bit dari Tabel. 2.5.16. (untuk tanda data) dan dari Tabel. 2.5.17. (untuk tanda perintah) bit fghj yang sesuai dengan arus positif or nilai negatif CRD. Artinya, CRD mempertahankan nilai sebelumnya.

Jika nilai pertidaksamaannya netral, maka saat mengkodekan blok HGF 3-bit dari Tabel. 2.5.16. (untuk tanda data) dan dari Tabel. 2.5.17. (untuk tanda

perintah), bit fghj yang sesuai dengan arus | |

diadopsi ketika memilih bit abcdei. |

4. Nilai bit abcdeifghj merupakan simbol dari tanda biner asli

5. Pertidaksamaan untuk karakter abcdeifghj dihitung.

6. Jika pertidaksamaan karakter abcdeifghj positif atau negatif, maka CRD karakter sebelumnya dibalik. Jika pertidaksamaan karakter abcdeifghj netral, maka nilai CRD karakter sebelumnya tetap dipertahankan.

tab. 2.5.16. Pengkodean 3-bit hingga 4-bit untuk karakter data

Nama byte | Tidak berkode | RD saat ini - fghj | RD + fghj . saat ini |

bit HGF | |||

tab. 2.5.17. Pengkodean 3-bit hingga 4-bit untuk karakter kontrol

Nama byte | Tidak berkode | RD saat ini - fghj | RD + fghj . saat ini |

bit HGF | |||

Beras. 2.5.17. menjelaskan logika di balik pengkodean urutan karakter 8b/10b

D10.3, D27.0, D23.7, K23.7, K28.5.

Kontrol pengkodean karakter

tab. 2.5.13. menggambarkan pengkodean karakter kontrol yang diadopsi dalam PCI-XP. Karakter-karakter ini tidak diacak oleh logika transmisi, tetapi mereka